1. The vacancy and apply

Of course, it all starts with the job vacancy. Does this one appeal to you? Then apply directly. Once we have received your application, we will contact you within a few working days for the next steps.

The project aims at extending the functional hardware description language Clash and the functional programming language Haskell with new features and capabilities for creating safe and secure, correct-by-design hardware, hardware-to-software interfaces and software. This includes the development and verification of an advanced IT system with non-trivial safety and security requirements for showcasing the aforementioned extensions.

PhD/MSc+

32 | 40 hours

Medior/Senior

€51,840 – €77,760 gross per year

As a formal verification engineer, you will play a crucial role in connecting existing verification technologies and methodologies with our Clash hardware design ecosystem and its mother language Haskell to be utilized for formal verification of hardware and software designs. While we realize everyone has their preferences and specializations, you are expected to work across the board, not shy away from technologies unknown to you and be at the office at least 2 days a week.

About you!

About us!

During the application process, we want to keep it as personal as possible, as it suits us best. If you have any questions during the process, feel free to email or call us! Of course, it depends on other candidates and how easy it is to schedule, but we aim to keep the entire process from dragging on for too long.

Of course, it all starts with the job vacancy. Does this one appeal to you? Then apply directly. Once we have received your application, we will contact you within a few working days for the next steps.

If we are impressed by your profile and background, we would like to invite you for a first interview. This will mainly be for getting to know each other, with two engineers from QBayLogic.

If you are still enthusiastic after the first interview and we believe you are a good fit for QBayLogic, then we would like to invite you for a second round. In this round, we will delve deeper, and your technical knowledge will be tested. This interview will also be longer than the first round and usually comes with an assignment that must be completed beforehand.

If the second interview goes well, we invite you for a day in the office where you get to work on small task together with your prospective colleagues.

If the day at the office is positive for both parties, then we would like to offer you a job. We will invite you again to discuss this and determine together when you can start.

Work situation

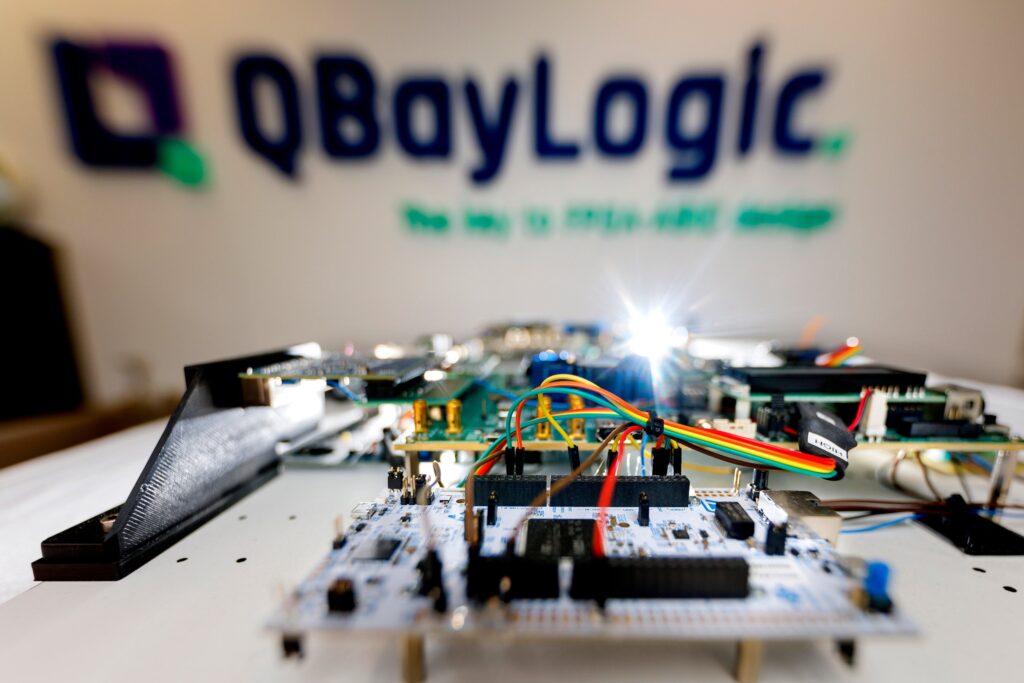

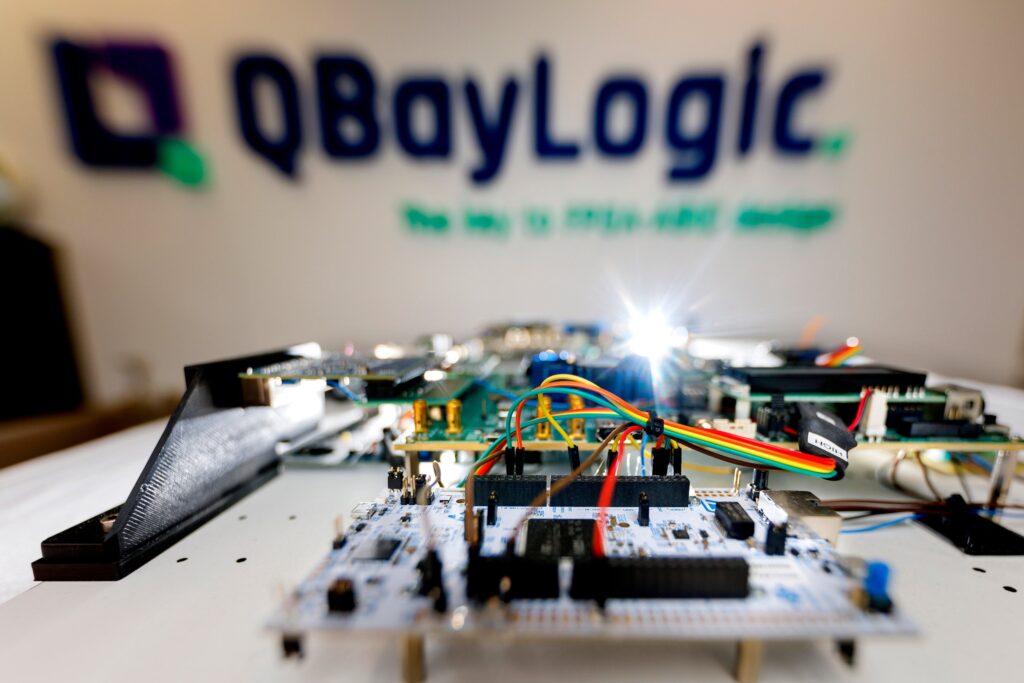

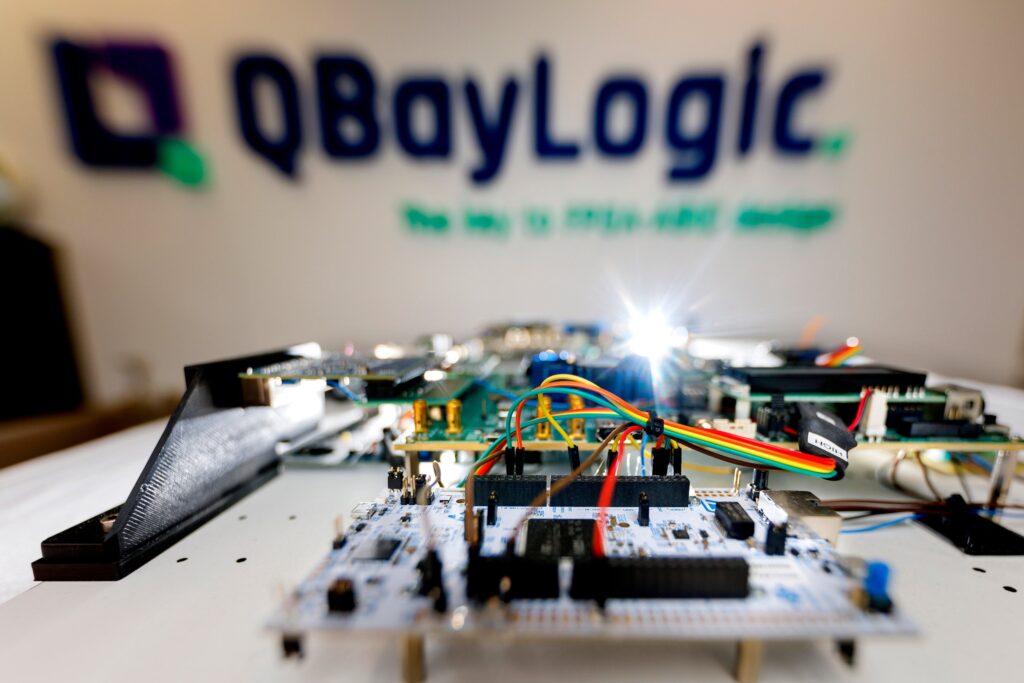

QBayLogic B.V. is an innovative FPGA/ASIC design company that is Steward Owned. With over nine years of experience in FPGA engineering, we assist businesses in creating high-speed, energy-efficient implementations of complex algorithms.

Our expertise spans various domains, including embedded systems, AI, edge computing, and data centers. What sets us apart is our commitment to open-source development, with the Clash compiler being our flagship project.

At QBayLogic, you become part of a team of 20 people that embraces challenges and pushes boundaries. You’ll become part of a team of people who are incredibly passionate about what they are developing. In a supportive environment, we foster continuous growth and encourage employees to develop their skills in FPGA engineering and open-source software development.

Or send me an email:

Apply here

Sollicitatie formulier