Getting started with Clash on the Arrow DECA devkit

Reading time: 14 minutes

It is now easier to get started with Clash on the Arrow DECA development kit. with the release of the DECA Starter Project.

The DECA development kit is an inexpensive ($37 ex. VAT at the time of writing) FPGA development kit with a lot of peripherals and has a decent-sized FPGA for many projects:

- FPGA Device

- MAX 10 10M50DAF484C6G Device

- Integrated dual ADCs, each ADC supports 1 dedicated analog input and 8 dual function pins

- 50K programmable logic elements

- 1,638 Kbits embedded memory

- 5,888 Kbits user flash memory

- 144 embedded 18×18 multipliers

- 4 PLLs

- Configuration and Debug

- Onboard USB-Blaster II (Mini USB type B connector)

- Memory devices

- 512 MB DDR3 SDRAM (16-bit data bus)

- 64 MB QSPI Flash

- Micro SD card socket

- Communication

- 10/100 Mbps Ethernet PHY with RJ45 connector

- USB 2.0 PHY with Mini USB type AB connector

- Connectors

- Two 46-pin BeagleBone expansion headers

- Two MAX 10 FPGA ADC SMA inputs

- Display

- HDMI TX, incorporates HDMI v1.4 features, including 3D video supporting

- Audio

- 24-bit CD-quality audio CODEC with line-in, line-out jacks

- Video Input

- MIPI CSI-2 camera interface (using a Hirose DF40C-30DS-0.4V receptacle, needs a DF40C-30DP-0.4V connector)

- Analog

- Two MAX 10 FPGA ADC SMA inputs

- Seven MAX 10 FPGA ADC inputs available on the BeagleBone expansion header

- Switches, Buttons, and Indicators

- 2 push-buttons

- 2 slide switches

- 8 blue user LEDs

- Sensors

- One proximity/ambient lighter sensor

- One humidity and temperature sensor

- One temperature sensor

- One accelerometer

- Two Capacitive touch sensor pads

- Power

- 5V DC input

Getting the starter project

If you haven’t already, install stack, a build tool for Haskell: https://docs.haskellstack.org/en/stable/README/. (In case you are a cabal-install or nix user, just follow the DECA starter project README from this point on: https://github.com/clash-lang/clash-starters/blob/main/deca/README.md)

Once stack is completely installed and on your PATH, you can now create a new Clash project for the DECA devkit using:

Where my-clash-deca-project is the name of the folder where the project will be created.

This will compile the src/DECA.hs Haskell/Clash source file to VHDL. If this is the first time you are building a Clash project using stack then this step will take some time as stack will install (from source) many of the project dependencies.

When all goes well, the last couple of lines in the terminal should read something in the spirit of:

Now that VHDL generation is finished, you can start Quartus Prime; once started, in the menu bar, click File -> Open Project and open syn/deca.qpf. In the menu bar, click: Processing -> Start Compilation. This can take up to a minute depending on your machine. If everything worked as it was supposed to work then the last messages in the logs should be in the spirit of:

Programming the FPGA

After synthesis has finished, it is time to program our FPGA board. Connect the FPGA board to a USB port, and start the programmer from the menu bar: Tools -> Programmer. Press the Start button on the left to program your FPGA and wait until the progress bar says 100% (Successful).

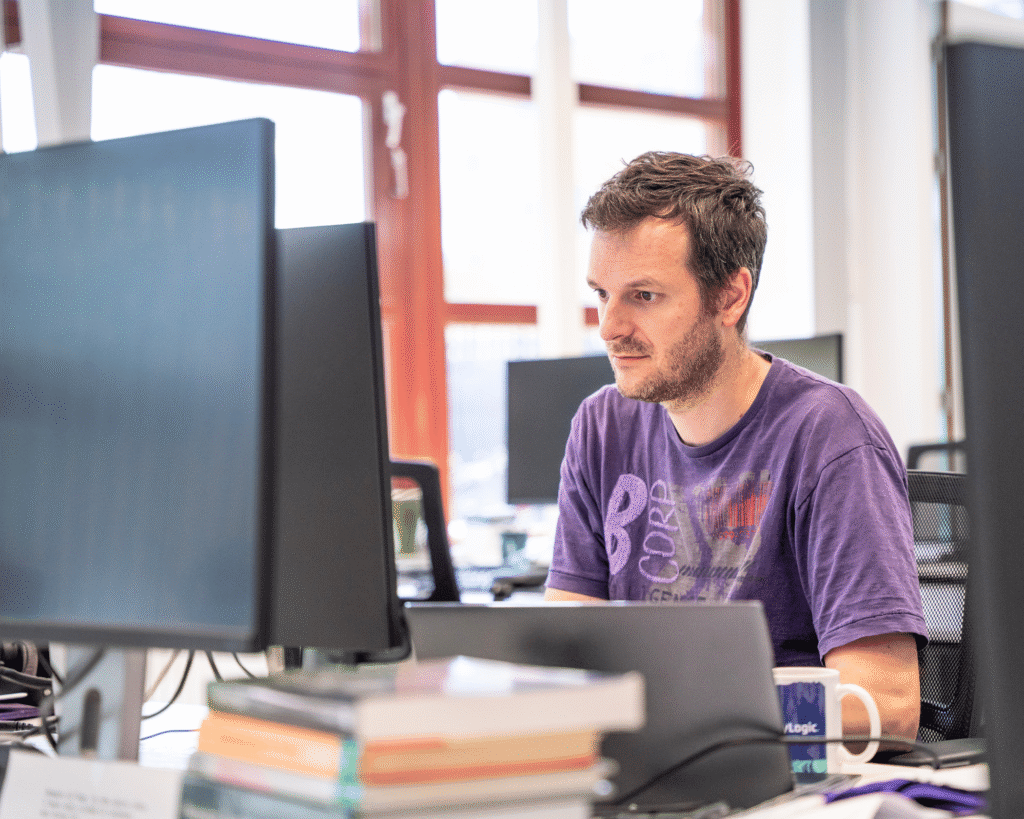

Once programmed, you should be able to operate the DECA devkit as seen here:

What’s next

Currently, the starter project is just a minor adaption of the blinker circuit described in the Clash FPGA starter blog post. The included README.md elaborates some more on the purpose of all the files in the project, and also repeats the above instructions on how to program the FPGA.

For now, the DECA starter project only connects the LEDs and the push-buttons. The intention is however to improve this DECA starter project over time and to add Clash descriptions that enable you to talk to all the other peripherals on the devkit.

|

1 |

stack new my-clash-deca-project clash-lang/deca |

|

1 |

stack run clash -- DECA --vhdl |

|

1 2 3 4 5 6 7 8 9 10 |

Registering library for my-clash-deca-project-0.1.. GHC: Parsing and optimising modules took: 0.730s GHC: Loading external modules from interface files took: 0.000s GHC: Parsing annotations took: 0.002s Clash: Parsing and compiling primitives took 0.140s GHC+Clash: Loading modules cumulatively took 1.207s Clash: Compiling DECA.deca Clash: Normalization took 0.019s Clash: Netlist generation took 0.003s Clash: Total compilation took 1.246s |

|

1 2 3 4 5 6 7 8 |

Info (332101): Design is fully constrained for setup requirements Info (332101): Design is fully constrained for hold requirements Info: Quartus Prime Timing Analyzer was successful. 0 errors, 2 warnings Info: Peak virtual memory: 550 megabytes Info: Processing ended: Tue Jun 1 09:51:50 2021 Info: Elapsed time: 00:00:01 Info: Total CPU time (on all processors): 00:00:01 Info (293000): Quartus Prime Full Compilation was successful. 0 errors, 11 warnings |