Axign – Audio chips for consumer electronics

Unlocking the next generation of audio chips with Axign and QBayLogic.

2022

High speed and low latency Ethernet traffic over a specialized optical fiber connection.

A client developing medical equipment required a solution that enabled multiple Ethernet streams over a specialized optical fiber connection. The specialized fiber connection only allowed a laser beam with a single wavelength, so wavelength multiplexing was not an option.

The specifications for the device asked for: an optical connection configurable at multiple Gbit/s speeds, a 10G/5G/2.5G Ethernet connection, multiple 1Gbit Ethernet connections, and an industrial 100Mbit EtherCAT connection. While all connections had end-to-end latency constraints, the latency constraint for the 100M EtherCAT connection was the most stringent at sub 1 microsecond end-to-end latency! As a custom ASIC was not a cost-viable solution, the device had to be made using off-the-shelf components. However, the bandwidth and latency requirements were so stringent that there was zero margin for overhead in every aspect of the design.

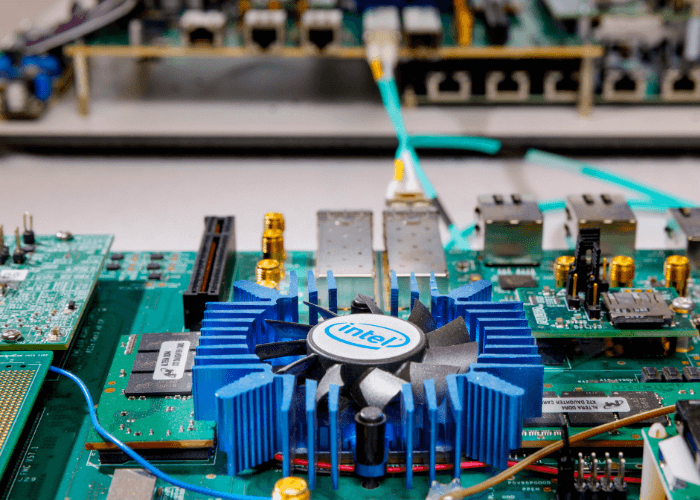

To validate whether a solution using off-the-shelf components was viable, QBayLogic, together with Demcon, created three pairs of prototype setups. These setups were created using readily available FPGA, Ethernet switching, and microcontroller development kits and daughter boards. Many optimizations were implemented at FPGA level. To minimize the latency in the datapath, optimizations have been performed on Ethernet communication levels, FIFOs and transceiver control.

QBayLogic developed the FPGA firmware for the prototype setups. The FPGA was responsible for multiplexing (and demultiplexing) the 10G/5G/2.5G Ethernet connection, two 1G Ethernet connections and the 100M EtherCAT connection over the optical fiber connection.

In order to meet both the bandwidth and latency requirements, the multiplexing logic in the FPGA had to combine both packet and circuit switching techniques.

With the prototype demonstrating the viability of the FPGA-based solution, the next step will be the development of a custom PCB, and porting the FPGA firmware to a smaller FPGA. These steps are required to meet the target size and unit cost of the final product.

In order to achieve the lowest possible latency, crucial for the application, a system level design approach was needed in order for the FPGA and Ethernet PHY chips to work in unison. The experts at QBayLogic have the expertise, from system-level to low-level digital design to tackle these problems, resulting in an optimal FPGA solution. Applications where the applied expertise would also fit: